아이테니엄

| |

| 생산 | 2001년 중반 ~ 2021년[1] |

|---|---|

| 주요 제조사 |

|

| 최대 CPU 클럭 속도 | 733 MHz ~ 1.73 GHz |

| FSB 속도 | 400 MT/s ~ 4.8 GT/s |

| 공정 | 65 ~ |

| 명령어 집합 | 아이테니엄 |

| 코어 | 1, 2, 4 |

| 코어 명칭 |

|

| 소켓 |

|

아이테니엄(Itanium)은 2001년에 공식 발표된 인텔이 제공하는 64비트 CPU이다. 휴렛 팩커드(HP)와 공동으로 개발된 높은 성능의 서버 아키텍처인 IA-64를 처음으로 채용하여, HP의 PA-RISC 프로세서를 대체하거나 인텔의 제온 프로세서의 규모로 사용되는 것을 목적으로 한다. 개발이 지연되면서 출시된 최초의 아이테니엄은 2001년에 출시되었다. 그 뒤로도 보다 강력한 아이테니엄 프로세서가 정기적으로 발표되었다. 아이테니엄은 2006년에 아이테니엄 2로 자리를 내 주었다.

인텔은 2019년 1월 30일 아이테니엄 CPU 계열의 수명 종료(EOL) 및 제품 생산 중단을 발표하였다.[1]

아이테니엄의 판매 추이

[편집]아이테니엄 프로세서는 그 능력면에서 지속적인 발전을 보여줘왔다. 머시드는 초기 개념을 증명하기 위한 제품이었지만, 맥킨리 프로세서는 메모리 구조를 극적으로 향상시켰으며 이로 인해 경쟁력있는 제품이 되었다. 매디슨은 130나노미터 공정기술로 전환을 하였으며 주된 성능의 병목현상을 극복시킬 수 있었던 캐시 크기를 증가시킬 수 있었다. 몬테시토는 90나노미터 공정기술로 듀얼코어를 가능하게 했으며 단위 전력당 성능을 크게 향상시킬 수 있었다. 몬트베일에서는 코어 수준 락스텝과 요구 기반 스위칭(Demand Based Switching, DBS)의 기능을 지원했으며 프론트 사이드 버스(FSB)를 667 MHz로 증가시키게 되었다. 아이테니엄 서버 판매의 추이 역사는 다음과 같다.[2][3]

아키텍처

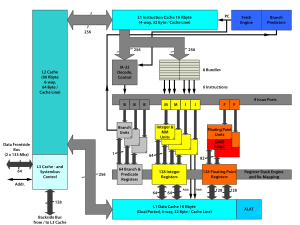

[편집]인텔은 아이테니엄 명령어 집합과 마이크로아키텍처에 대해서 자세한 정보를 공개하고 있으며[4] 기술에 대한 개요들도 제공하고 있다. 아키텍처의 이름은 그동안 여러번 바뀌었다. HP는 처음 PA-WideWord라고 명명했으나 인텔은 나중에 IA-64라고 이름을 지었다. 그 이후 아이테니엄 프로세서 아키텍처(IPA)라고 불리다가 최종적으로 인텔 아이테니엄 아키텍처라고 명명했다.[5] 그렇지만 일반적으로 IA-64라고도 불린다. 인텔 아이테니엄 아키텍처는 폭넓은 64비트 함축적인 병렬 아키텍처이다. 기본 데이터 워드는 64비트이며 바이트 단위로 액세스 가능한 바이트-어드레싱을 지원한다. 논리적인 주소 범위는 264 바이트이다. 아키텍처는 predication speculation과 분기 예측을 지원한다. 하드웨어적인 레지스터 재명명을 사용한다. 루프의 병렬적인 실행을 위해서도 동일한 방법이 사용된다. Speculation, 예측, predication, 그리고 재명명(renaming)은 컴파일러에 의해 제어된다. 각 명령어 워드는 이것들을 위해 추가적인 비트가 있다. 이 방법은 아키텍처의 뚜렷한 특성이다. 아키텍처는 128개의 정수용 레지스터와 128개의 부동소수점 레지스터, 64개의 1비트 예측 레지스터, 그리고 8개의 분기 레지스터가 있다. 부동소수점 레지스터는 82비트 길이여서 중간 결과를 정확하게 보존할 수 있다.

명령어 실행

[편집]각 128비트의 명령어 워드에는 3개의 명령어가 포함된다. 명령어를 가지고 오는 페치(Fetch)부에서는 클럭당 두개의 워드를 L1캐시로부터 파이프라인으로 읽어올 수 있다. 컴파일러가 이러한 최대의 장점을 살리게 되면, 프로세서는 클럭 주기동안 여섯개의 명령어를 실행할 수 있다. 프로세서는 11개의 그룹에 총 30개의 기능 실행부를 가지고 있다. 각 부분은 특정 부분집합의 명령어 집합을 실행할 수 있으며 각 유닛은 실행부분이 데이터를 기다리기위해 멈추지 않는한 단위 주기당 하나의 명령어의 비율로 실행을 한다. 그룹에 있는 모든 유닛들이 명령어 집합의 부분집합과 정확히 일치하지는 않지만 공통된 명령어는 여러 유닛들을 실행될 수 있다. 실행 유닛 그룹은 아래와 같이 구성되어 있다.

- 6개의 범용 ALU, 2 정수처리부, 1 이동부(shift)

- 4개의 데이터 캐시 부

- 6개의 멀티미디어 부, 2 병렬 이동 부, 1 병렬 곱, 1 population count

- 2개의 실수연산 곱셈-누산기, 2 SIMD 실수연산 곱셈-누산기 부(각 2개의 32비트 동작)[6]

- 3개의 분기 유닛

컴파일러는 명령어들을 동시에 실행할 수 있는 6개의 집합으로 집단을 만든다. 부동소수점 유닛은 곱셈과 누산을 동시에 실행할 수 있어서 하나의 부동소수점 명령어는 곱셈을 한후 덧셈이 필요한 경우 두개의 명령어처리를 한번에 수행할 수 있다. 이러한 연산은 과학 계산과 같은 곳에서는 매우 일반적이며 곱셈-누산기는 성능향상에 커다란 도움을 준다. 이러한 경우 프로세서는 하나의 주기동안에 4개의 FLOPs를 처리할 수 있다. 예를 들면 800MHz 아이테니엄 프로세서는 3.2GFlops의 이론 성능을 가진다. 가장 빠른 아이테니엄 2 1.67GHz의 이론 성능은 6.67GFlops이다.

메모리 아키텍처

[편집]2002년부터 2006년까지 아이테니엄2 프로세서는 공통의 캐시 계층구조를 공유하여 왔다. 16KiB의 1차 명령어 캐시와 16KiB의 1차 데이터 캐시를 가지고 있다. 2차 캐시는 명령어와 데이터용 공통의 통합 캐시로서 256KiB의 크기이다. 3차 캐시도 역시 공통의 통합 캐시이지만 그 크기는 1.5MiB에서부터 24MiB로 다양하다. 256KiB의 2차 캐시는 주 산술 논리 장치(ALU)를 방해하지 않고 세마포어 연산을 처리할 수 있는 충분한 회로를 포함하고 있다. 주 메모리는 버스를 통하여 별도 칩으로 접근할 수 있다. 아이테니엄 2 버스는 초기에 맥킨리 버스라 불리었다. 그렇지만 일반적으로 아이테니엄 버스라 통칭된다. 버스의 속도는 새로운 프로세서가 출시될 때마다 지속적으로 빨라졌으며 버스 전송은 단위 클럭 주기당 2x128비트이다. 따라서 200MHz 맥킨리 버스의 전송 속도는 6.4GiB/s이며 533MHz 몬테시토 버스 전송속도는 17.056 GiB/s이다.[7]

아키텍처 변경

[편집]2006년 이전 출시된 아이테니엄 프로세서는 IA-32 아키텍처를 하드웨어적으로 구현하였기 때문에 기존의 32비트 서버 애플리케이션들을 지원한다. 그렇지만 IA-32코드의 성능은 아이테니엄 프로세서의 64비트뿐만 아니라 그 당시의 x86프로세서보다 뒤떨어졌다. 2005년에 인텔은 IA-32 실행 계층( IA-32 Execution Layer,IA-32 EL)를 개발하였다. 이것은 더 나은 성능을 제공하는 소프트웨어 애뮬레이션이다. 따라서 인텔은 몬테시토에서부터 IA-32 코드의 하드웨어적인 지원을 하지 않았다. 인텔은 2006년 출시된 몬테시토에서 기본적인 프로세서의 마이크로아키텍처 향상을 이루었다.

- 하드웨어 멀티스레딩 : 각 프로세서 코어는 두개의 실행 스레드를 위한 콘텍스트를 가진다. 하나의 스레드가 메모리 접근을 위해 대기하고 있을 때, 다른 스레드는 실행을 할 수 있다. 인텔은 이것을 x86과 x86-64 마이크로프로세서에서 지원하는 하이퍼 스레딩과 구분을 하기 위해서 “굵은 멀티스레딩”(coarse multithreading)이라고 불렀다. 굵은 멀티스레딩은 인텔 아이테니엄 아키텍처와 조화를 잘 이루어서 좋은 성능 향상을 가져왔다.

- 가상화를 위한 하드웨어 지원 : 인텔은 가상화의 핵심 기능들을 하드웨어적으로 지원하는 인텔 가상화 기술(인텔 VT-i)를 추가하였다. 가상화는 소프트웨어 “하이퍼바이저”가 프로세서 위에서 여러 운영 체제가 동시에 동작할 수 있도록 한다.

- 캐시 향상 : 몬테시토는 이전의 공용 L2 캐시를 명령어만을 위한 1MiB L2 캐시와 데이터 전용 256KiB L2 캐시로 분리하였다. 몬테시토는 최대 12MiB의 공통 L3 캐시를 지원한다. 또한 캐시 안정성 향상을 위한 기술로 인텔 캐시 안전 기술(Intel Cache Safe Technology)을 지원하여 캐시에서 발생할 수 있는 데이터 오류를 최소화할 수 있다.

출시된 프로세서

[편집]

아이테니엄 프로세서는 그 능력면에서 지속적인 발전을 보여줘왔다. 머시드는 초기 개념을 증명하기 위한 제품이었지만, 맥킨리 프로세서는 메모리 구조를 극적으로 향상시켰으며 이로 인해 경쟁력있는 제품이 되었다. 매디슨은 130나노미터 공정기술로 전환을 하였으며 주된 성능의 병목현상을 극복시킬 수 있었던 캐시 크기를 증가시킬 수 있었다. 몬테시토는 90나노미터 공정기술로 듀얼코어를 가능하게 했으며 단위 전력당 성능을 크게 향상시킬 수 있었다. 몬트베일에서는 코어 수준 락스텝과 요구 기반 스위칭의 기능을 지원했으며 프론트 사이드 버스를 667 MHz로 증가시키게 되었다.

| 코드네임 | 공정기술 | 공개일 | 클럭 | L2 캐시/ 코어 |

L3 캐시/ 코어 |

버스 | 다이/ 장치 |

코어/ 다이 |

W/ 장치 |

설명 |

|---|---|---|---|---|---|---|---|---|---|---|

| 아이테니엄 | ||||||||||

| 머시드 |

180 나노미터 | 2001-06 | 733 MHz | 96 KiB | 없음 | 266 MHz | 1 | 1 | 116 | 2 MiB 오프다이 L3 캐시 |

| 800 MHz | 130 | 4 MiB 오프다이 L3 캐시 | ||||||||

| 아이테니엄 2 | ||||||||||

| 맥킨리 |

180 나노미터 | 2002-07-08 | 900 MHz | 256 KiB | 1.5 MiB | 400 MHz | 1 | 1 | 130 | HW 브렌치롱(branchlong) |

| 1 GHz | 3 MiB | 130 | ||||||||

| 매디슨 |

130 나노미터 | 2003-06-30 | 1.3 GHz | 3 MiB | 130 | |||||

| 1.4 GHz | 4 MiB | 130 | ||||||||

| 1.5 GHz | 6 MiB | 130 | ||||||||

| 2003-09-08 | 1.4 GHz | 1.5 MiB | 130 | |||||||

| 2004-04 | 1.4 GHz | 3 MiB | 130 | |||||||

| 1.6 GHz | ||||||||||

| 디어필드 | 2003-09-08 | 1.0 GHz | 1.5 MiB | 62 | 낮은 전압 | |||||

| 혼도[8] | 2004-Q1 | 1.1 GHz | 4 MiB | 400 MHz | 2 | 1 | 260 | 32 MiB L4 | ||

| 팬우드 |

2004-11-08 | 1.6 GHz | 3 MiB | 533 MHz | 1 | 1 | 130 | |||

| 1.3 GHz | 400 MHz | 62? | 낮은 전압 | |||||||

| 매디슨 |

2004-11-08 | 1.6 GHz | 9 MiB | 400 MHz | 130 | |||||

| 2005-07-05 | 1.67 GHz | 6 MiB | 667 MHz | 130 | ||||||

| 2005-07-18 | 1.67 GHz | 9 MiB | 667 MHz | 130 | ||||||

| 아이테니엄 2 9000 계열 | ||||||||||

| 몬테시토 |

90 나노미터 | 2006-07-18 | 1.4 GHz | 256 KiB(D)+ 1 MiB(I) |

6-24 MiB | 400 MHz | 1 | 2 | 104 | 가상화, 멀티스레드, IA-32 하드웨어 없음 |

| 1.6 GHz | 533 MHz | |||||||||

| 아이테니엄 2 9100 계열 | ||||||||||

| 몬트베일 |

90 나노미터 | 2007-10-31 | 1.42-1.66 GHz | 256 KiB(D)+ 1 MiB(I) |

8-24 MiB | 400-667 MHz | 1 | 1-2 | 75-104 | 코어 수준의 락스텝, 요구 기반 스위칭 |

| 아이테니엄 9300 계열 | ||||||||||

| 투킬라 | 65 nm | 2010-02-08 | 1.33-1.73 GHz | 256 KiB (D)+ 512 KiB (I) |

10-24 MB | 4.8GT/s QPI | 1 | 2–4 | 130–185 | FSB를 대체하는 새로운 점대점 프로세서 QPI 상호연결버스. 인텔 터보 부스트 |

앞으로 출시될 프로세서

[편집]폴손

[편집]폴손은 투킬라 프로세서의 후속 모델로서 2012년에 출시 예정이다.[9] 인텔에 의하면 45나노미터 공정기술을 건너뛰고 바로 32나노미터 공정기술을 사용할 것이다. 8코어 이상과 멀티스레딩 향상, 그리고 특히 가상화에서 병렬화의 장점을 살릴 수 있는 새로운 명령어들을 지원할 예정이다. 폴손은 세계 최대의 48MiB L3캐시와 코어당 768KiB 총 6MiB의 L2 캐시, 총 캐시 크기는 54MiB이며 다이 사이즈는 544 mm²로서 이전 세대인 투킬라 프로세서의 698.75 mm² 보다 작을것으로 예상된다.[10]

키슨

[편집]키슨은 2014년에 출시될 폴손의 후속 아이테니엄 프로세서이다. 폴손과 키슨 그리고 투킬라는 이진, 소켓 호환성을 지원할 것이다라는 것외에는 알려진 것이 없다.

같이 보기

[편집]참조

[편집]- ↑ 가 나 “Select Intel Itanium Processors and Intel Scalable Memory Buffer, PCN 116733-00, Product Discontinuance, End of Life” (PDF). Intel. 2019년 1월 30일.

- ↑ “Mining Itanium”. 《CNet News》. 2005년 12월 7일. 2007년 3월 19일에 확인함.

- ↑ Bailey, Michelle, et.al. (February 2006). “Customer Perceptions of the Future of Itanium” (PDF). 《IDC》. 2007년 6월 15일에 원본 문서 (PDF)에서 보존된 문서. 2007년 3월 22일에 확인함.

- ↑ “Intel Itanium Processor Manuals”. 《인텔 web site》. 2007년 6월 22일에 원본 문서에서 보존된 문서. 2007년 5월 16일에 확인함.

- ↑ “HPWorks Newsletter”. 2001년 9월. 2008년 11월 20일에 원본 문서에서 보존된 문서. 2008년 1월 24일에 확인함.

- ↑ Sharangpani, Harsh; Arora, Ken (2000). "Itanium Processor Microarchitecture". IEEE Micro. pp. 38–39.

- ↑ Cataldo, Anthony (2001년 8월 30일). “Intel outfits Itanium processor for faster runs”. 《EE Times》. 2010년 2월 1일에 원본 문서에서 보존된 문서. 2007년 12월 6일에 확인함.

- ↑ http://www.theregister.co.uk/2004/05/06/hp_mx2_itaniummodule/

- ↑ http://www.eweek.com/c/a/IT-Infrastructure/New-Intel-Itanium-Offers-Greater-Performance-Memory-Capacity-349863/1/[깨진 링크(과거 내용 찾기)]

- ↑ “Researchers carve CPU into plastic foil”. Eetimes.com. 2010년 12월 9일에 원본 문서에서 보존된 문서. 2010년 12월 19일에 확인함.

외부 링크

[편집]- 아이테니엄

- 공식 웹사이트

- 공식 웹사이트