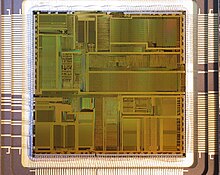

P5 (마이크로아키텍처)

최초의 펜티엄 마이크로프로세서는 1993년 3월 22일 인텔이 선보였다.[1][2] P5라는 이름의 마이크로아키텍처는 인텔의 5세대이자 최초의 슈퍼스칼라 IA-32 마이크로아키텍처이다.

코어와 스테핑[편집]

펜티엄은 1990년대 중반 동안 개인용 컴퓨터를 위한 인텔의 주요 마이크로프로세서였다. 초기 디자인은 새로운 프로세서에서 다시 구현되었으며 경쟁력뿐 아니라 개인용 컴퓨터와 같은 특화된 시장을 유지하기 위해 새로운 기능들이 추가되었다. 그 결과, P5 마이크로아키텍처에는 다양한 종류가 생겨났다.

- P5

- P54C

- P54CQS

- P54CS

- P24T

- P55C

- 틸라묵(Tillamook)

각주[편집]

- ↑ 《View Processors Chronologically by Date of Introduction:》, Intel, 2007년 8월 14일에 확인함

- ↑ 《Intel Pentium Processor Family》, Intel, 2007년 8월 14일에 확인함

외부 링크[편집]

- (영어) CPU-Collection.de - Intel Pentium images and descriptions

인텔 데이터시트[편집]

- (영어) Pentium (P5)

- (영어) Pentium (P54)

- (영어) Pentium MMX (P55C)

- (영어) Mobile Pentium MMX (P55C)

- (영어) Mobile Pentium MMX (Tillamook)

| 이 글은 컴퓨터 과학에 관한 토막글입니다. 여러분의 지식으로 알차게 문서를 완성해 갑시다. |