애슬론

| 생산 | 2018년 9월 6일 |

|---|---|

| 주요 제조사 | |

| 최대 CPU 클럭 속도 | ~ 3.5 GHz |

| 공정 | 0.25μm ~ 7 nm |

| 명령어 집합 | x86 또는 x86-64 |

| 마이크로아키텍처 | Zen (Radeon Graphics 내장) Zen+ (Radeon 그래픽스 내장) Zen2 (Radeon 그래픽스 내장) |

| 코어 명칭 |

|

| 이전 모델 | Athlon Classic Athlon Thunderbird Athlon XP/MP Athlon 64 Athlon 64 X2 Athlon X2 Athlon II |

애슬론(Athlon)은 미국 AMD사에서 만든 제7 세대의 중앙처리장치의 1 시리즈이다.

최초의 애슬론, 즉 애슬론 클래식은 "제7 세대" x86 프로세서 중 최초의 것이었다. 애슬론이 처음 나왔을 무렵부터 상당 기간, 애슬론은 인텔의 동급 CPU보다 성능이 우월하였다. AMD는, 애슬론이라는 브랜드 이름을 애슬론 64로 계승시켜 나갔는데, 애슬론 64는 x86-64 (AMD64) 기술을 적용한 8세대 프로세서였다.

1999년 6월 23일, 애슬론은 시장에 첫 선을 보였다. 애슬론은 데카슬론(decathlon)의 줄임말이었는데, 이는 "우승자/혹은 경기의 우승 트로피"를 의미하는 고대 그리스어였다.

배경

[편집]AMD의 전직 CEO이자 창업주인 제리 샌더스는 1990년대 후반, K6 아키텍처의 성공을 기반으로 하여 PC 시장에서의 AMD 사의 점유율을 높이고자, 전략적 합작을 추구하였다. 그 중 주요한 파트너십은 1998년 발표된 AMD와 반도체 업계의 거목 모토로라와의 합작이었다.[1] 이 합작 발표에서, 제리 샌더스는 이 합작의 목적이 "가상의 고릴라"을 만들어서 재정적으로 불리하여 새로운 설비를 쑥쑥 만들어나갈 수 없는 AMD로 하여금 인텔과 반도체 제조 역량 면에서 경쟁할 수 있도록 하는 것이라고 언급하였다. 이 합작은 공동으로 구리 반도체 기술을 개발해 나간다는 항목을 포함하고 있었다. 이것은 K7의 생산 프로세스에서 결정적인 역할을 해냈다.

1999년 6월, AMD는 애슬론 (K7) 프로세서를 출시하였다. 애슬론 프로세서의 디자인 팀은 더크 메이어가 이끌었다. 그는 알파 프로세서 프로젝트의 수석 디자이너 중 하나였다. 제리 샌더스는, DEC가 그 프로젝트를 무효화하자, DEC 엔지니어들에게 접근하여 AMD에서 일할 것을 종용하였다. 제리 샌더스는, 엔지니어링 전문가들로 이루어진 팀을 거의 통째로 스카웃해올 수 있었다. 이들은 AMD의 AMD K5 및 AMD K6을 개발했던 노련한 엔지니어들과 조화를 이루었다.

모토로라와 합작함으로써, AMD는 인텔보다 거의 1년 앞서, 구리 연결(interconnect) 제조 기술을 정밀하게 가다듬어 바로 칩을 생산할 수 있을 정도로 만들 수 있었다. 이 개선된 공정을 사용하여 180 나노미터 프로세서를 생산해낼 수 있었다. 부수적으로 다이 크기가 줄어들자(die-shrink), 애슬론이 상대적으로 적은 전력을 소모할 수 있게 됐으며, 그 덕에 애슬론 클럭 속도를 1 GHz까지 높일 수 있었다.[2]. 새로운 공정의 수율은 예상 외로 높았다. 2000년 3월까지 칩을 대량으로 생산해냈다.

일반 아키텍처

[편집]

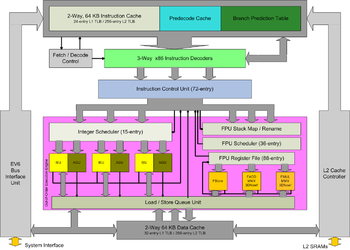

내부적으로, 애슬론은 완전한 7세대 x86 프로세서이자, 7세대 x86 프로세서 중 최초의 프로세서이다. AMD K5와 K6와 마찬가지로, 애슬론은 x86 명령어를 런타임에 디코드하여 애슬론 고유의 내부 명령어로 바꾸어 실행하는 RISC 마이크로프로세서이다. 애슬론은 아웃-오브-오더 디자인이다. 이 점은 예전의 후반 5x86 AMD CPU와 마찬가지이다. 애슬론은 DDR SDRAM 메모리 기술이 활용된 DEC 알파 EV6 프론트 사이드 버스 아키텍처를 이용하였는데, 이는 100 MHz 애슬론 프론트 사이드 버스는 실제로 200 MHz 싱글 데이터 레이트 버스와 같은 레이트로 데이터를 주고받는 말이 된다. (이를 다시 말해 200 MT/s (초당 트랜스퍼)라고 일컫는다.) 당시 SDR 100내지 133 MHz 버스를 사용하던 인텐의 펜티엄 III와 비교해 보면, AMD 쪽이 훨씬 향상된 것이었다.

AMD는 K6보다 더욱 강건한(robust) x86 명령어 디코딩 성능을 내도록 CPU를 디자인하였다. 한 번에 취급 중인 데이터(data in-flight)를 더 많이 갖고 있을 수 있도록 하였다. 애슬론의 CISC 투(to) RISC 디코더 트리플릿(triplet)은 한 클럭 당 최대 6개의 x86 명령어를 디코딩할 수 있었다. 비록 현실 세계(real world)에서는 잘 일어나지 않는 일이지만 말이다.[3] 파이프라인을 유휴 없이 사용하게 만드는 데에 결정적인 역할을 하는 중요한 분기 예측 장치(critical branch predictor unit)는 K6에 들어간 것보다 향상된 것이었다. 빠른 클럭 속도를 내기 위해 더 깊이 있고 더 많은 단계를 갖춘 파이프라이닝을 하였다.[4] 반면에 180 nm 공정에서도, AMD K6-III+는 겨우 570 MHz를 기록했을 뿐인데, 이것은 파이프라인이 짧았기 때문이었다. 애슬론은 이것보다 훨씬 향상되었다.

애슬론이 나오기 이전까지는, 오랫동안 부동소수점 x87 처리 성능은 AMD가 인텔에 뒤진다고 알려져 왔다. 하지만 AMD는, 애슬론에 와서, 꽤 인상적인 슈퍼-파이프라인드, 아웃-오브-오더(out-of-order), 트리플-이슈(triple-issue) 부동소수점 장치를 구현함으로써 이 논란을 불식시켰다.[3] 부동소수점 장치의 세 유닛(unit) 각각은 약간의 리던던시(redundancy)를 가지면서 최적화된 종류의 명령어를 수행할 수 있도록 딱 맞추어졌다. 분리된 장치들을 가지게 됨으로써, 한 클럭 당 한 개 이상의 부동소수점 명령어를 수행할 수 있게 되었다.[3] 이 FPU는 AMD에서는 엄청난 발전이었다. K6 FPU는 인텔 P6 FPU에 비해서는 뒤쳐졌었으나, AMD는 애슬론을 출시함으로써 인텔을 앞설 수 있었다.[5]

애슬론에는 3DNow! 부동소수점 SIMD 기술이, 역시, 들어가 있었다. 약간의 변경(revision)을 거친 것이었으며, 이름은 "인핸스트 쓰리디나우!"(Enhanced 3dNow!)로 바뀌었다. 추가적으로 디지털 신호 처리(DSP) 명령어와 인텔 SSE의 서브셋인 확장-MMX (명령어 집합) (extended-MMX (명령어 집합))의 구현이 들어가 있었다.[6]

애슬론의 온보드 CPU 캐시는 전형적이게도 L1, L2 두 개의 레벨(level)로 구성되어 있다. 애슬론은 128 KiB 스플릿(split) 레벨 1 캐시를 갖춘 최초의 x86 프로세서였다. 2-웨이 어소시에이티브 캐시(나중에는 16-웨이가 됨.)는 각각 데이터와 명령어를 위한 2×64 KiB로 나뉘었다(하버드 아키텍처).[3] 이 캐시는 K6에 들어간 크기(2×32 KiB 캐시를 갖춤)의 두 배였으며, 펜티엄 II 및 III에 들어간 2×16 KiB L1 캐시의 네 배 크기였다. 초창기 애슬론(애슬론 슬롯 A, 나중에 애슬론 클래식이라는 이름이 붙음)은 512 KiB짜리 레벨 2 캐시를 사용하였다. 이는 CPU와 분리되어 있었고, 프로세서 카트리지 보드(cartridge board)에 붙어 있었으며, 코어 속도의 33% 내지 50%의 속도록 동작하였다. 250 nm 제조 공정이 비용 대비 효용이 높은(cost-effective) 다이 크기를 유지하면서 온-다이 캐시를 허용하기에는 너무 컸기 때문이었다. 이후, 애슬론 CPU는 작아진 제조공정 덕분에 낮아진 트랜지스터 제조 단가 덕을 봤다. 요컨데, 180 nm 및 130 nm 제조 공정 덕분에 온-다이 L2 캐시는 풀 CPU 클럭 속도에서 동작하는 캐시가 되었다.

애슬론

[편집]애슬론 클래식

[편집]

애슬론 클래식은 1999년 6월 23일 발매되었다. 모든 벤치마크(benchmark)에서, 펜티엄 III에 비해, 월등한 성능을 보여주었다.[7]

애슬론 클래식은 카트리지(cartridge) 형태의 프로세서였다. 이 디자인은 슬롯 A라고 불렸으며, 펜티엄 II나 펜티엄 III에 사용되었던 슬롯 1의 디자인과 매우 유사하였다. 사실은,경쟁사의 CPU였던 인텔 CPU에 사용되었던 슬롯 부품과 똑같은 것을 사용하였다. (마더보드 제조사들이 비용을 절감할 수 있도록 하기 위해) 하지만 사용자들이 엉뚱한 CPU를 꼽는 것을 방지하기 위해 방향을 위-아래로 바꾸어버렸다. (인텔 슬롯과의 시그널-호환성은 사라졌다.(signal incompatible)) 마더보드 상에 캐시 메모리를 장착하는 것에 비해 카트리지 안에 더 빠른 속도의 캐시 메모리를 장착할 수 있었다. 펜티엄 II 및 "카트마이"-코어 펜티엄 III와 마찬가지로, 애슬론 클래식은 512KiB 2차 캐시를 장착하였다. 이 캐시는, 인텔의 것과 마찬가지로, 코어 클럭에 대한 분수 비율(즉 몇 분의 일, fraction)에서 동작하였으며, 고유의 64 비트짜리 버스를 가지고 있었다. 버스의 이름은 "백 사이드 버스"였는데, 동시적인(concurrent) 시스템 프로트 사이드 버스 및 캐시 액세스를 가능케 하였다.[8] 초창기에는, L2 캐시는 CPU 클럭 속도의 반 클럭 속도로 설정되어 있었으며, 최대 700 MHz까지 동작하였다. 더 빨라진 슬롯-A 프로세서가 나오자, 캐시 클럭은 2/5 (최대 850 MHz) 혹은 1/3 (최대 1 GHz)이 되었다.[9] 당시, 시중에 나와 있던 SRAM들은 애슬론의 클럭 스케일러빌리티(scalability)를 지원하지 못하였다. 캐시 칩 기술에 기술적으로 한계가 있었고, 그렇게 고속으로 캐시가 동작하기에는 일렉트릭컬/캐시 레이턴시 같은 것들에서 곤란함이 존재하였었다.

슬롯-A 애슬론은 AMD에서 나온 최초의 배수-잠금(multiplier-locked, 다른 말로 배수 락) CPU이다. 전 세계적으로 은밀한 조직에 의해 CPU 리마킹이 성행하던 시기였는데, 배수-잠금은 부분적인 이유에서는 이것을 막기 위함이었다. 슬롯-A 애슬론 이전의 AMD CPU들은 사용자가 마더보드 상에서 설정한 클럭이면 아무 클럭이든 동작하였으며, CPU의 상표를 다시 붙여 더 빠른 속도의 CPU라고 속여 파는 것은 매우 쉬운 일이었다. 이렇게 상표가 다시 붙은 CPU들은, 오버클럭킹되고 제대로 테스트 안 된 까닭에, 가끔 불안정해졌으며, AMD의 명성에 먹칠을 하고 있었다. 비록 애슬론의 배수(multiplier)가 잠겼지만, 솜씨 좋은 컴퓨터 하드웨어 마니아들은 카트리지의 PCB 상에서 배수(multiplier)를 제어할 수 있는 커넥터를 발견해내었다. 끝내는 CPU의 배수 잠금을 풀 수 있는 "골드핑거"(goldfingers device, 장치가 붙는 프로세서 보드 상의 금색 커넥터 패드에서 이름을 땄다.)라는 장치가 고안되기도 하였다.[10]

상업적으로, AMD 애슬론 클래식은 대성공이었다 - 애슬론 그 자체도 좋은 제품이었지만, 당시 경쟁사 인텔이 심각한 제조, 설계, 품질 이슈를 겪고 있었기 때문이기도 하였다. 특히, 인텔은, 180 nm 제조 공정으로 옮겨가고 있는 과정에서, 1999년 후반부터 2000년 중반까지, 지연을 겼었다. 펜티엄 III 부품은 부족하였다. 반면,눈에 띄게도, 매우 부드러운 공정 간 전환을 해냈으며, 풍부한 재료 공급을 받고 있었다. 애슬론 판매고는 꽤 높았다.

- 상세 사양

- K7 "아르곤 Argon" (250 nm)

- K75 "플루토/오라이언 Pluto/Orion" (180 nm)

- L1-캐시: 64 + 64 KiB (데이터 + 명령어s)

- L2-캐시: 512 KiB, CPU 모듈 상의 외부 칩 형태로 들어감. CPU 클럭 속도의 50, 40, 33% 속도.

- MMX (명령어 집합), 3DNow!

- 슬롯 A (EV6)

- 프론트 사이드 버스: 200 MT/s (100 MHz 더블 펌프드 double-pumped)

- VCore: 1.6 V (K7), 1.6 - 1.8 V (K75)

- 최초 발매일 : 1999년 6월 23일 (K7), 1999년 11월 29일 (K75)

- 클럭 속도 : 500-700 MHz (K7), 550-1000 MHz (K75)

선더버드 (T-Bird)

[편집]

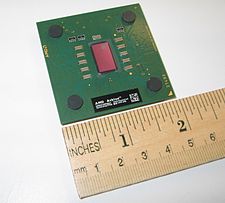

애슬론의 제2 세대 칩인 "선더버드"(Thunderbird)는 2000년 6월 5일 발매되었다. 선더버드는 전통적인 핀 그리드 어래이(PGA) 형태로 출시되었으며, 주기판 상의 소켓 A에 꼽는 형태였다. 또한 슬롯 A 패키지로도 존재하였다. CPU 클럭 속도는 600 내지 1400 MHz였다. 애슬론 클래식과의 주요 차이점은 캐시 디자인이었다. 인텔이 예전 카트마이 펜티엄 III를 더 빠른 코퍼마인 P-III으로 대체할 때 작업한 내용과 비슷하게도, AMD는 애슬론 클래식의 512 KiB 외부 감속된(reduced speed) 캐시를, 온-칩, 풀-스피드 익스클루시브(exclusive) 캐시로 대체하였다. 일반적으로, 캐시가 많을수록 성능은 올라가고, 또한 캐시 속도가 빠를수록 성능이 또한 향상된다.[11]

선더버드에 와서 AMD는 캐시 디자인을 크게 바꾸었다. 예전의 애슬론 클래식 CPU에서는, CPU 캐싱은 인클루시브 디자인이었으며, L1 안에 있는 데이터는 L2 캐시에서도 중복되었다. (duplicated) 선더버드에 와서는 익스클루시브 디자인으로 바뀌었다. L1 캐시의 내용(content)는 L2 캐시에서 중복되지 않았다. 이에 따라 총합 캐시 크기가 늘어났으며, 요컨데 하나의 매우 크기가 큰 L1 캐시가 있는데, 속도가 빠른 영역 (L1 캐시), 속도가 느린 영역 (L2 캐시)가 있는 것처럼 효율적으로 동작하였다.[12] 애슬론의 L1 캐시 크기가 컸고 또한 익스클루시브 디자인이 채택되었으므로, L2 캐시는 기본적으로 "빅팀 캐시"처럼 쓰이게 되었으며, L2 캐시가 성능이 높아야 하거나 크기가 커야 한다는 요구가 사라지게 되었다. AMD는 예전 애슬론의 64 비트짜리 L2 캐시 데이터 버스를 계속 이용하였다. 그 결과로 인해, 비교적 높은 레이턴시(latency)를 갖게 되었다. 간단해진 L2 캐시 덕분에, L2 캐시가 클록 스케일링이나 일드(yield) 이슈를 낼 가능성이 줄어들었다. 예전 애슬론에 쓰였던 2-웨이 어소시에이티브 스킴 대신에, 더 효율적인 16-웨이 어소시에이티브 레이아웃을 사용하였다.[11]

10년 전의 Am386DX-40 이래로, AMD 사에서 선더버드는 가장 성공적인 제품이었다. 당시는 주기판 설계 기술이 한창 향상되고 있던 시기였으며, 처음에는 아주 소량의 애슬론주기판을 찍어내던 주기판 제조 회사들이 점점 많아져, 거의 모든 주요 주기판 제조 회사들이 애슬론 주기판을 생산하기에 이르렀다. 드레스덴에 들어선 AMD의 새로운 팹이 가동을 시작하였다. 이에 애슬론 생산량을 늘어났으며, 공정 기술의 향상이 이루어져, 구리 연결(interconnect)로 전환되었다. 2000년 10월, 애슬론 "C"가 발매되었다. 주기판 프론트 사이드 버스 속도가 133 MHz (266 MT/s)로 높아졌으며, 선더버드 "B" 모델보다 클럭 당 10%의 추가 성능 향상이 있었다.

- 상세 사양

- L1-캐시: 64 + 64 KiB (데이터 + 명령어)

- L2-캐시: 256 KiB, 풀 스피드

- MMX (명령어 집합), 3DNow!

- 슬롯 A & 소켓 A (EV6)

- 프론트 사이드 버스: 100 MHz (Slot-A, B-models), 133 MHz (C-models) (200, 266 MT/s)

- VCore: 1.7 V - 1.75 V

- 최초 발매일: 2000년 6월 5일

- 클럭 속도:

애슬론 XP/MP

[편집]성능적인 면에서, 선더버드는 라이벌이었던 펜티엄 III를 완전히 물리쳤다. 초창기 펜티엄 4도 성능 측면에서 저만치 뒤떨어져 있었다. 하지만 펜티엄 4도 성능이 점점 향상되어갔다. 1.7 GHz P4 (2001년 4월)가 발매되고 나서는 선더버드가 더 이상 성능적인 우위에 있다고 말하기가 어려워졌다. 선더버드 디자인에, 열 발생과 전력 소모 이슈가 있어서 선더버드로 하여금 1400 MHz 이상의 클럭으로 동작하게 하는 것은 사실상 어려웠다. (1400 MHz 클럭에서조차도 좀 뜨거웠다.)

팔로미노

[편집]

애슬론의 제3 세대 칩인 "팔로미노"(Palomino)는 2001년 10월 9일 발매되었다. 코드네임(codename)이 "팔로미노"였으며, 상품명은 애슬론 XP(Athlon XP)였다. 애슬론 XP는 PR 레이팅 체계를 갖고 마케팅되었는데, 애슬론의 성능을 "선더버드" 코어의 그것과 비교하는 시스템이었다. (1600+ 같은 단어가 붙는다는 말이다.)

애슬론 XP는 클럭 속도가 1333 내지 1533 MHz이었으며, PR 레이팅은 1500+ 내지 1800+였다. 발매 시점에서, AMD가 이 새로운 코어를 출시함으로써, 1800+ 모델을 가지고 당시 성능으로 따져서 가장 우위에 있는 x86을 보유하게 되었다. 또한 한 달 뒤, 1600 MHz 1900+를 출시함으로써 그 격차를 더 벌리게 되었다.[13] 뒤에 붙는 "XP"라는 단어는 eXtreme Performance라는 것을 의미하는데, 윈도우 XP의 경우를 비공식적으로 참조한 것이었다.[14]

팔로미노는 펜티엄 III에서 가져온 풀 스트리밍 SIMD 확장(SSE)를 탑재한 최초의 K7 코어였다. 또한 AMD의 3DNow! Professional도 탑재하였다. 선더버드와 비교해서, 같은 클럭 속도에서 대략 10%정도 빨랐다. 새로운 SIMD 기능과 여러 가지 개선 때문이었다. 이 코어는 K7의 트랜슬레이션 룩어사이드 버퍼(TLB) 아키텍처를 개선하였으며, 하드웨어적 데이터 프리페치 메커니즘을 추가하여 가용한 메모리 밴드위스를 더 잘 활용하게 하였다.[15]

또한, 코어 레이아웃을 바꿔서, 전력 소모가 줄어들었는데, 예전보다 20%가 줄었으며 또한 열 발생도 그런 정도로 줄어들었다.[16] 애슬론 "선더버드"가 1400 MHz 클럭 속도에서 한계를 보인 데 반해, 팔로미노에 와서, 트랜지스터 레이아웃을 바꾸고 전력 소모를 줄인 덕분에, 같은 180 nm 제조 공정 및 같은 코어 전압 하에서도, 팔로미노는 클럭 속도를 높여나갈 수 있었다.

사실, "팔로미노"는 모바일 버전으로 먼저 발매되었다. 이름은 "모바일 애슬론 4"였다(코드네임은 "코베트 Corvette"였다.).[15] 팔로미노는 공식적으로 듀얼프로세싱(dual processing)을 지원하였는데, 이 버전의 이름은 애슬론 MP였다.[17]

- 상세 사양

- L1-캐시: 64 + 64 KiB (데이터 + 명령어)

- L2-캐시: 256 KiB, 풀 스피드

- MMX (명령어 집합), 3DNow!, SSE

- 소켓 A (EV6)

- 프론트 사이드 버스: 133 MHz (266 MT/s)

- VCore: 1.75 V

- 최초 발매일: 2001년 10월 9일

- 클럭 속도:

- A4: 850-1400 MHz

- XP: 1333-1733 MHz (1500+ to 2100+)

- MP: 1000 - 1733 MHz

쏘로브레드 (T-Bred)

[편집]

애슬론의 제4 세대 칩인 "쏘로브레드"(Thoroughbred, 다른 말로 "써로우브레드", "쏘러브레드", "서러브레드")는 2002년 6월 10일 발매되었다. 1.8 GHz 코어 클럭이었으며, PR 레이팅 시스템 상으로는 2200+ 이었다. AMD로서는 최초의 130 nm 제조 공정 프로세서였다. 180 nm 프로세서에 비해 다이 크기 절감이 있었다.

쏘로브레드 코어에는 두 가지 버전이 있다. 보통 쏘로브레드 A, 쏘로브레드 B라 불린다. A 버전은 초기에 1800 MHz 클럭으로 도입되었고, 클럭 스케일러빌리티를 제한하는 열발생 및 디자인 이슈가 있었다. 사실, AMD는 클럭 속도를 팔로미노의 최상급 프로세서만큼 올릴 수 없었다. 팔로미노 코어를 대체하는 식으로, 1333 to 1800 MHz 클럭 버전만이 출시되었다. 쏘로브레드 B 버전은 추가적인 메탈 레이어를 갖고 있어서, 더 높은 클럭 속도에 도달할 수 있었다. B 버전은 더 높은 클럭 속도로 출시되었다.

새로운 제조 공정에도 불구하고, 쏘로브레드는 "팔로미노"와 모든 면에서 유사하였다. 쏘로브레드가 시중에 나와 있을 때, 쏘로브레드 라인의 프론트 사이드 버스 클럭이 향상되었는데, 266 MT/s 내지 최대 333 MT/s 까지였다. 이것 때문에 프로세서 메모리 및 I/O 액세스의 효율성이 높아졌고, 클럭 당 성능이 좋아졌다. AMD는 그들의 PR 레이팅 스킴을 바꾸었는데, 낮은 클럭 속도가 더 높은 PR 레이팅에 대응되게 하였다.

- 상세 사양

- L1-캐시: 64 + 64 KiB (데이터 + 명령어)

- L2-캐시: 256 KiB, 풀 스피드

- MMX (명령어 집합), 3DNow!, SSE

- 소켓 A (EV6)

- 프론트 사이드 버스: 133/166 MHz (266/333 MT/초)

- VCore: 1.5 V - 1.65 V

- 최초 발매일: 2002년 6월 10일 (A), 2002년 8월 21일 (B)

- 클럭 속도:

- T-Bred "A": 1400-1800 MHz (1600+ to 2200+)

- T-Bred "B": 1400-2250 MHz (1600+ to 2800+)

- 133 MHz FSB: 1400-2133 MHz (1600+ to 2600+)

- 166 MHz FSB: 2083-2250 MHz (2600+ to 2800+)

바톤과 쏘톤

[편집]애슬론의 제4 세대 칩인 "바톤"(Barton 바튼[*])은 2003년 초 출시되었다. PR 레이팅은 2500+, 2600+, 2800+, 3000+ 및 3200+이었다. "쏘로브레드" 코어 프로세서보다 높은 클럭에서 동작하지는 않았지만, 총합 512 KiB L2 캐시 및 (일부 모델에서, 기존보다 빠른) 400 MT/s 프론트 사이드 버스를 탑재함으로써, PR 레이팅이 올라갔다.[18] "쏘톤"(쏘튼) 코어는 "바톤" 코어의 변형버전이었다. 바톤이었는데, L2 캐시의 절반이 동작하지 않게 한 것이었고, 쏘로브레드 코어와 기능상으로는 동일하게 동작하였다.

바톤이 나올 무렵, "노스우드"(Notrthwood) 펜티엄 4가 나와 있었고, AMD의 프로세서보다 경쟁력이 있었다.[19] 유감스럽게도, 인텔 라인에서 그랬던 것만큼, 512 KiB로 L2 캐시 크기를 늘린 일이, AMD 프로세서에는 그다지 큰 향상을 가져다 주지 못했다. 겨우 몇 퍼센트 정도의 클럭-당 성능 향상이 얻어졌을 뿐이었다.[18] PR 레이팅은 이제 뭔가 부정확한 것이 되었다. 몇몇 낮은 클럭의 바톤 모델들이 높은 클럭 및 낮은 PR 레이팅을 갖는 쏘로브레드 프로세를 성능 면에서 능가하지 못하게 되었기 때문이었다.[19]

다른 하나의 개선점은 400 MT/s 버스 클럭이었다. 바톤의 효율성이 높아지긴 하였다. 하지만, 당시 인텔의 쿼드-펌프드(quad-pumped) 버스가 AMD의 더블-펌프드 EV6 버스보다 스케일링(scaling) 잘 된다고 하는 사실이 명백하였다. 펜티엄 4의 800 MT/s는 애슬론이 전혀 따라갈 수 없었다. 같은 밴드위스 레벨을 달성하고자 한다면, 애슬론 버스가 달성할 수 없는 클럭 속도로 동작했어야 했기 때문이었다.[18]

K7 아키텍처는 이제 그 한계점에 다다랐었다. 인텔이 그들의 프로세서 성능을 향상시키는 바를 따라잡으려면, AMD는 그들의 프로세서 디자인을 처음부터 완전히 뒤바꿔야 했다.[18] AMD는 곧 애슬론 64의 출시를 준비하고 있었다.

- 상세 사양

바톤 (130 nm)

- L1-캐시: 64 + 64 KiB (데이터 + 명령어s)

- L2-캐시: 512 KiB, 풀 스피드

- MMX (명령어 집합), 3DNow!, SSE

- 소켓 A (EV6)

- 프론트 사이드 버스: 166/200 MHz (333/400 MT/s)

- VCore: 1.65 V

- 최초 발매일: 2003년 2월 10일

- 클럭 속도: 1833-2333 MHz (2500+ to 3200+)

- 166 MHz FSB: 1833-2333 MHz (2500+ to 3200+)

- 200 MHz FSB: 2100, 2200 MHz (3000+, 3200+)

쏘톤 (130 nm)

- L1-캐시: 64 + 64 KiB (데이터 + 명령어s)

- L2-캐시: 256 KiB, 풀 스피드

- MMX (명령어 집합), 3DNow!, SSE

- 소켓 A (EV6)

- Front side bus 프론트 사이드 버스: 133/166/200 MHz (266/333/400 MT/s)

- VCore: 1.5 V - 1.65 V

- 최초 발매일: 2003년 9월

- 클럭 속도: 1667-2200 MHz (2000+ to 3100+)

- 133 MHz FSB: 1600 - 2133 MHz (2000+ to 2600+)

- 166 MHz FSB: 2083 MHz (2600+)

- 200 MHz FSB: 2200 MHz (3100+)

모바일 애슬론 XP

[편집]

모바일 애슬론 XP(Athlon XP-M)는 보통의 애슬론 XP와 동일한 프로세서로서, 낮은 전압에서 동작하고, 대개 낮은 버스 속도에서 동작하며, CPU 배수 잠금이 되어 있지 않다는 점에서만 차이나는 프로세서였다. 낮은 Vcore 전압 덕분에, CPU는 전력 소모를 줄일 수 있었으며(축전지로 동작하는 랩탑 컴퓨터에 알맞다.) 발열을 줄일 수 있었다. 애슬론 XP-M CPU는 또한 높은 정도의 발열 허용 범위(tolerance)를 갖고 있었는데, 이는 노트북 PC에서는 꽤 타이트한 요구 조건 사항이었다.

애슬론 XP-M은 예전의 모바일 애슬론 4를 대체하였다. 모바일 애슬론 4는 구식 "팔로미노" 코어를 사용하고 있었다. 애슬론 XP-M은 "쏘로브레드"나 "바톤" 코어를 사용하였다. 일부 저-전력XP-M은 일반적인 소켓 A 대신 마이크로PGA 소켓 563을 사용하였다.

예전의 모바일 K6+ 프로세서들처럼, 애슬론 XP-M은 저전력 소모를 위한 동적 클럭 조정이 가능하였다. 시스템인 유휴 상태에 진입하면, CPU 클럭 자체가 낮은 버스 배수(multiplier)를 이용해 낮아지며, 전압도 낮아진다. 이후, 프로그램이 다시 계산을 요구하는 작업을 시작하면, CPU는, 요구를 들어주기 위해, 재빨리 (약간의 레이턴시는 있음) 중간 정도 혹은 최대의 속도를 낸다. 이 기술은 "PowerNow!"라는 이름으로 마케팅되었다. 인텔의 스피드스텝 전력 절감 기술과 비슷했다. 이 기능은 CPU, 바이오스 및 운영 체제에 의해 제어되었다. AMD는 나중에, K8 기반 CPU ( 애슬론 64 등)에 와서, 이 기술을 Cool'n'Quiet라는 이름으로 바꾸었는데, 데스크톱 PC에도 사용되도록 꾸민 것이었다.

애슬론 XP-M은 언더클럭킹 뿐만 아니라 데스크톱 오버클럭킹에 사용되어 인기 있었다. 낮은 전압 요구 사양과 높은 발열 레이팅 요구 사양을 만족시키기 위해 CPU가 제조 라인에서 좋은 것이 골라져 나왔기 (체리 피킹) 때문이었다. 제조 라인 중 가장 좋은 코어만 골라져 나온 덕분에, 이 CPU들은 (데스크톱쪽 CPU들보다) 더 믿음직하게 오버클럭될 수 있었다. 또한, 단일 배수(multiplier)로 잠금되어있지 않았기 때문에, 오버클럭킹 절차도 간단하였다. 일부 애슬론 XP-M "바톤" 코어는 최대 3.1 GHz까지 오버클럭될 수 있었다.

애슬론 XP-M은 또한 언더클럭킹 기능애문에 선호되었다. 언더클럭킹은 기본적으로 주어진 클럭 속도에 대해 CPU가 안정되게 작동할 수 있는 최소의 전압 Vcore를 찾는 일이다. 애슬론 XP-M CPU는 데스크톱 버전보다 비교적 낮은 전압에서 동작하였다. 이러한 까닭들 때문에, 고성능이자 저전력 CPU였던 애슬론 XP-M CPU는 홈 씨어터 PC 등에 많이 쓰였다.

애슬론의 경쟁 CPU

[편집]애슬론 상표를 사용한 다른 모델

[편집]애슬론 XP와 MP까지는 K7 아키텍처였으나 애슬론 64부터는 K8 아키텍처임에도 애슬론 상표를 사용한다.

슈퍼컴퓨터

[편집]다음은 AthlonMP에 기반한 가장 빠른 슈퍼컴퓨터이다.

- Rutgers University, Department of Physics & Astronomy. Machine: NOW Cluster - AMD Athlon. CPU: 512 AthlonMP (1.65 GHz). Rmax: 794 Gigaflops.

같이 보기

[편집]각주

[편집]- ↑ “MOTOROLA PREPARES TO MANUFACTURE AMD'S UPCOMING K7 CHIP”. HP. 1998년 8월 7일. 2007년 9월 28일에 원본 문서에서 보존된 문서. 2007년 6월 30일에 확인함.

- ↑

“AMD Announces First Revenue Shipments From Dresden "MEGAFAB"”. AMD Press Release. 2000년 7월 5일.

|제목=에 지움 문자가 있음(위치 1) (도움말) - ↑ 가 나 다 라 Hsieh, Paul. “7th Generation CPU Comparisons”.

- ↑ De Gelas, Johan (1999년 9월 29일). “The Secrets of High Performance CPUs, Part 1”. Ace's Hardware. 2001년 11월 24일에 원본 문서에서 보존된 문서. 2007년 12월 15일에 확인함.

- ↑ Pabst, Thomas (1999년 8월 23일). “Performance-Showdown between Athlon and Pentium III”. 《Tom's Hardware》.[깨진 링크(과거 내용 찾기)]

- ↑ Womack, Tom. “Extensions to the x86 architecture”. 2012년 1월 15일에 원본 문서에서 보존된 문서. 2012년 1월 6일에 확인함.

- ↑ Lal Shimpi, Anand (1999년 8월 9일). “AMD Athlon”.

- ↑ De Gelas, Johan (1999년 9월 29일). “Clash of Silicon, The Athlon 650”. 《Ace's Hardware》. 2004년 12월 4일에 원본 문서에서 보존된 문서. 2007년 12월 15일에 확인함.

- ↑ Lal Shimpi, Anand (2000년 3월 6일). “AMD Athlon 1 GHz, 950 MHz, 900MHz”. Anandtech.

- ↑ Noonan, Jim and Rolfe, James. “Athlon Gold-Finger Devices”. 《Overclockers.com.au》. 2009년 2월 1일에 원본 문서에서 보존된 문서. 2012년 1월 6일에 확인함.

- ↑ 가 나 “K7 microarchitecture information”. 《Sandpile.org》. 1999년 10월 13일에 원본 문서에서 보존된 문서. 2012년 1월 6일에 확인함.

- ↑ Stokes, John (2005년 2월 1일). “Inside AMD's Hammer: the 64-bit architecture behind the Opteron and Athlon 64”. Ars Technica. 9 February 1, 2005쪽.

- ↑ Wasson, Scott (2001년 11월 5일). “AMD's Athlon XP 1900+ processor: Pouring it on”. 《The Tech Report》. 2006년 11월 27일에 원본 문서에서 보존된 문서. 2007년 12월 15일에 확인함.

- ↑ Advanced Micro Devices, Inc. “Introducing the AMD Athlon XP Processor” (PDF).

- ↑ 가 나 Lal Shimpi, Anand (2001년 5월 14일). “AMD Athlon 4 - The Palomino is Here”. 《Anandtech》. 4-5쪽.

- ↑ Wasson, Scott (2001년 10월 9일). “AMD's Athlon XP 1800+ processor: 1533 > 1800”. 《The Tech Report》. 2007년 5월 21일에 원본 문서에서 보존된 문서. 2007년 12월 15일에 확인함.

- ↑ Lal Shimpi, Anand (2001년 6월 5일). “AMD 760MP & Athlon MP - Dual Processor Heaven”. 《Anandtech》.

- ↑ 가 나 다 라 De Gelas, Johan (2003년 2월 10일). “Barton: 512 KB Athlon XP Reviewed”. 《Ace's Hardware》. 2007년 6월 7일에 원본 문서에서 보존된 문서. 2007년 12월 15일에 확인함.

- ↑ 가 나 Lal Shimpi, Anand. (2003년 2월 10일). “AMD's Athlon XP 3000+: Barton cuts it close”. 《AnandTech》.

외부 링크

[편집]- (영어) cpu-collection.de AMD Athlon processor images and descriptions

- (영어) amdboard.com AMD Athlon/Duron/Sempron CPU identification and OPN breakdown

- (영어) AMD의 기술적 상세 사양 - 7세대 CPU(들)에 대해서.(.pdf)

- (영어) Easy identification with Interactive AMD product ID

- (영어) AMD 애슬론의 기술적 상세 사양