무어의 법칙

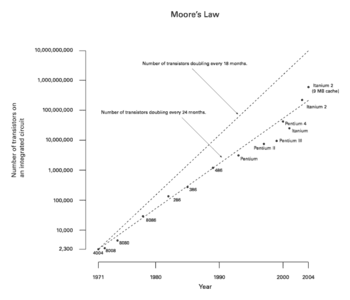

무어의 법칙(영어: Moore's law)은 반도체 집적회로의 성능이 24개월마다 2배로 증가한다는 법칙이다. 경험적인 관찰에 바탕을 두고 있다. 인텔의 공동 설립자인 고든 무어가 1965년에 내 놓은 것이다.

| “ |

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer. 부품 제조 비용이 최소가 되는 복잡함은 해마다 대략 2배의 비율로 증가해 왔다. 단기적으로는 이 증가율이 올라가지 않아도, 현상을 유지하는 것은 확실하다. 적어도 앞으로 10년 동안 거의 일정한 비율을 유지할 수 없다고 믿을 이유는 없으나 보다 장기적으로는 증가율은 조금 불확실하다. 이 말은 1975년까지는 최소 비용으로 얻을 수 있는 집적회로의 부품 수는 65,000개에 이를 것이다. 나는 그 만큼의 대규모 회로를 1 개의 회로판 위에 구축할 수 있을 거라고 믿는다. |

” |

— 1965년 4월 19일, 일렉트로닉스 (잡지)에 실린 논문 "Cramming more components onto integrated circuits"

|

고든 무어의 의견은 무어 자신이 "법칙"이라고 이름을 붙인 것이 아니라 캘리포니아 공과대학의 교수와, 대규모LSI의 파이오니아 실업가의 카버 미드에 따른 것이다.

무어는 오늘의 기계식 마우스의 공동 발명자인 더글라스로부터, 1960년의 강의에 대해 집적회로의 크기 축소의 전망에 대해 논의한 것을 들었을지도 모른다. 1975년에는 무어는 앞으로 2년마다 2배의 속도밖에 되지 않을 것이라고 말할 계획을 세웠다. 그는 자신이 "18 개월마다"라고 한 적은 한 번도 없는데, 그렇게 인용되었던 것이라고 굳게 주장하고 있다. 2005년 무어의 발표 후 현재는 사실상 무어의 법칙이 의미가 없다.

무어의 법칙의 3가지 조건[편집]

무어의 법칙의 세 가지 조건은 다음과 같다.[1]

- 반도체 메모리칩의 성능 즉, 메모리의 용량이나 CPU의 속도가 18개월에서 24개월마다 2배씩 향상된다는 '기술 개발 속도에 관한 법칙'이다.

- 컴퓨팅 성능은 18개월마다 2배씩 향상된다.

- 컴퓨터 가격은 18개월마다 반으로 떨어진다다

같이 보기[편집]

각주[편집]

- ↑ Laudon, Kenneth C, Jane P. 《Management Information Systems 12/E: Managing the Digital Firm, CHAPTER 5, 201P》. Pearson Education Asia. ISBN-10 : 027375453X / ISBN-13 : 9780273754534.

| 이 글은 컴퓨터 과학에 관한 토막글입니다. 여러분의 지식으로 알차게 문서를 완성해 갑시다. |