NAND 게이트

| INPUT | OUTPUT | |

| A | B | A NAND B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

디지털 회로 분야에서 NAND 게이트(negative-AND)는 모든 입력이 참일 때에만 거짓인 출력을 내보내는 논리 회로이다.

함수 NAND(a1, a2, ..., an)는 NOT(a1 AND a2 AND ... AND an)와 논리적으로 동일하다.

기호[편집]

NAND 게이트에는 3가지 기호가 있다: MIL/미국 국립 표준 협회 기호, IEC 기호, 현재는 사용이 권장되지 않는 DIN 기호 (오래된 도식에서 볼 수 있음). 더 많은 정보는 논리 회로 문서를 참조. NAND 게이트의 ANSI 기호가 도치 버블(inversion bubble)이 연결된 표준 AND 게이트이다.

|

|

|

| MIL/ANSI 기호 | IEC 기호 | DIN 기호 |

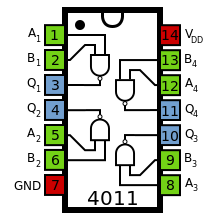

하드웨어 기술 및 핀[편집]

NAND 게이트는 기본 논리 게이트이고, TTL과 CMOS IC에서도 마찬가지로 기본 게이트로서 사용된다.

구현[편집]

|

|

|

|

|

|

같이 보기[편집]

외부 링크[편집]

- TTL NAND and AND gates - All About Circuits