주소 디코더

보이기

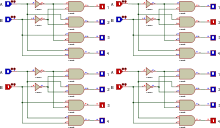

디지털 공학에서 주소 디코더, 번지 디코더, 번지 해독기, 어드레스 디코더(address decoder)는 둘 이상의 주소 비트용 입력과 하나 이상의 장치 선택 신호용 출력을 지니는 바이너리 디코더이다.[1] 특정 장치 주소가 주소 입력에 나타나면 디코더는 해당 장치의 선택 출력을 표명(assert)한다. 단일 출력의 전용 주소 디코더를 주소 버스상의 개별 장치에 연동할 수 있고, 아니면 하나의 단일 주소 디코더가 여러 대의 장치에 서비스를 제공할 수 있다.[2]

n개의 주소 입력 비트가 있는 단일 주소 디코더는 최대 n대의 장치를 서비스할 수 있다. 7400 시리즈의 집적 회로의 일부 멤버들은 주소 디코더로 사용이 가능하다. 이를테면 주소 디코더로 사용 시 74154[3]는 4개의 주소 입력과 16개(예: 24)의 장치 선택기 출력을 제공한다. 주소 디코더는 주소 디코딩 외의 다른 수많은 용도를 지닌 디멀티플렉서(demux)라는 이름의 바이너리 디코더를 이용한 것이다.

주소 디코더들은 버스를 이용하는 시스템에 중요한 구성 요소이다. 이들은 모든 집적 회로 계열 및 프로세서, 그리고 모든 표준 FPGA 및 ASIC 라이브러리에 사용된다. 디지털 논리 디자인의 입문 교과서에서 다루기도 한다.[1]

각주

[편집]- ↑ 가 나 Paul Horowitz and Winfield Hill (1989). 《The Art of Electronics》 2판. Cambridge University Press. 685,766쪽. ISBN 978-0-521-37095-0.

- ↑ S. J. Cahill (1993). 《Digital and microprocessor engineering》 2판. Ellis Horwood. 489–494쪽. ISBN 978-0-13-213398-2.

- ↑ Datasheet for 74HC154