연산 증폭기

연산 증폭기(op-amp, Operational amplifier)는 두 개의 차동 입력과, 대개 한 개의 단일 출력을 가지는 직류 연결형(DC-coupled) 고이득 전압 증폭기이다.[1] 하나의 연산 증폭기는 그 입력 단자 간의 전위차보다 대개 백배에서 수 천배 큰 출력 전압을 생성한다.[2]

연산증폭기는 다양한 종류의 전자 회로에서 중요한 구성 요소(building block)이다. 연산증폭기는 그 기원이 선형, 비선형, 주파수 의존 회로에 쓰이던 아날로그 컴퓨터에 있다. 이득과 같은 최종 요소의 특성이, 온도 변화와 op-amp 자체의 불균일한 제조상태에 거의 의존하지 않고, 외부 부품(component)에 의해서 설정되기 때문에 회로 설계에서 인기가 있다.

연산증폭기는 오늘날 가장 널리 쓰이는 전자 부품 중의 하나이며, 소비자 디바이스, 산업용 디바이스, 공학용 디바이스로 다양하게 쓰이고 있다. 많은 표준적인 IC 연산증폭기의 가격은 일반적인 생산품에서는 몇 센트 수준이다. 그러나 특별한 기능을 가진 집적화된 연산증폭기, 또는 하이브리드 연산증폭기는 소량 주문시 100 달러(미국) 이상의 수준이다. 연산증폭기는 단일 부품으로서 패키지되기도 하고, 복잡한 집적회로의 요소로서 쓰이기도 한다.

다른 종류의 차동증폭기는 Fully differential amplifier (연산증폭기와 비슷하지만, 출력이 두개), Instrumentation amplifier (대개 세개의 연산증폭기로 구성됨), 절연 증폭기 (isolation amplifier, instrumentation amplifier와 비슷하지만, 일반적인 연산증폭기를 손상시킬수 있는 전압에 대해 저항력이 있음), negative feedback amplifier (대개 하나 이상의 연산증폭기와 저항 피드백 네트워크로 구성됨)가 있다.

회로 표기

[편집]

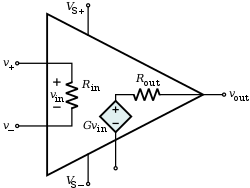

연산 증폭기의 회로 표현은 우측 그림과 같다. 각 기호의 의미는 다음과 같다.

- : 비반전 신호 입력

- : 반전 신호 입력

- : 출력

- : 양의 전원 공급 전압

- : 음의 전원 공급 전압

회로의 해석 과정에 중요한 영향을 미치지 않을 경우 공급 전압 기호는 생략되는 경우가 있다.

연산 증폭기 특성

[편집]이상적 연산증폭기(Ideal op-amp)

[편집]이상 연산증폭기는 가장 이상적으로 동작하는 목표 증폭기이다. 증폭기의 설계에서 이상적으로 특성을 설정하고 제품을 만들 때, 이상적 특성에 가깝게 만드는 것이 목표이기도 하다.

이상적 연산 증폭기는 다음 특성을 갖는다.

연산 증폭기를 사용하여 증폭기를 만들 때, 이득이 무한대 이므로 주로 되먹임 회로에 의해 원하는 이득을 얻는다.

이상 연산증폭기의 특성을 반영하여 다음 2가지 특성을 규정한다:

- 과 사이의 전압은 0으로 전압이 같다. =0 : 열린 이득 G=∞.

- 에 들어가는 전류는 0이다 : 입력 임피던스 Rin=∞.

위의 두 가지 조건을 종종 가상 접지(virtual-ground)라고 한다. 접지라는 말은 에 되먹임 회로가 입력되고, 에 실제 접지가 연결되었을 때는 가상이라는 말을 붙일 필요가 없다. 그러나 단일전원공급을 사용하는 경우나 이중전원공급에서 특정 입력전압에 오프셋 전압을 인가할 때, 실제로 에 실제 접지가 아니라 특정 고정 전압을 입력할 수도 있기 때문에 신호 입장에서의 기준전압 0V(신호 측면의 ground)가 필요한데 이것을 가상 접지라고 한다. 연산 증폭기를 사용해서 회로를 설계할 때, 대부분은 양전원과 음전원을 사용한다. 이렇게 되면 단자는 Vs+, Vs-, GND(기준접압 0)을 사용한다. 이렇게 되면 신호의 GND와 전원의 GND가 같기 때문에 가상 접지를 고민할 필요가 없다. 어느 경우든, 첫 번째 조건은 '과 의 전압이 같다'라는 의미가 중요하다.

이 개념은 연산증폭기 회로해석에서 중요한 특징이 된다.

연산 증폭기 응용 회로

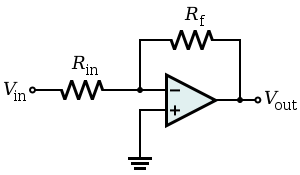

[편집]반전 증폭기(Inverting amplifier)

[편집]

반전 증폭기는 입력된 신호에 대해 정해진 증폭도로 신호가 반전되어 출력되는 증폭기이다. 음전압은 양전압으로, 양전압은 음전압으로 신호의 모양은 유지하면서 증폭된다.

반전 증폭기의 이득을 구하기 위해 회로에서 방정식을 세우면:

전압 V−는 Vout과 Vin 사이의 Rf과 Rin에 의한 전압 분배 형태이다. 따라서 V− 전압 형태로 방정식을 세우면 :

이득 방정식 Vout 구하기 위해 V−을 치환하면:

여기서 가 매우 크면(이상적 연산 증폭기는 무한대) 다음과 같이 근사화 시킬수 있다:

비반전 전압 입력 과 GND 사이에 저항을 삽입하는 경우가 있는 이것은 바이어스 전류에 의한 입력 옵셋 전압의 다른 전압 강하를 줄이는데 목적이 있다. 또 어떤 연산 증폭기의 신호 왜곡을 줄이는데 사용하기도 한다.

연산증폭기의 특성을 이용한 이득 해석(Gain analysis through characteristic of op-amp)

[편집]

연산 증폭기의 특징인 입력단자 V+와 V-에 흘러 들어가는 입력 전류는 0이고, V+와 V-의 전압은 같다. 따라서 회로에서 Rin과 Rf에 흐르는 전류는 같다. V- = V+ = 0, =0 이므로 V- 노드에서 KCL 방정식을 세우면:

이 방정식을 이득을 얻기 위한 방정식으로 풀면:

연산증폭기의 입력 단자에 흐르는 전류는 이상적인 경우 0이다. 그러나 실제로 소자에 따라 다르지만 극히 적은량의 전류가 흐르므로 완전히 0은 아니다. 따라서 이 이득은 단자에 흐르는 전류의 크기에 따라 오차를 갖는 근사치이다.

비반전 증폭기(Non-inverting amplifier)

[편집]

연산 증폭기의 특징인 입력단자 V+와 V-에 흘러 들어가는 입력 전류는 0이고, V+와 V-의 전압은 같다. 따라서 회로에서 Vin=V+= V- 같고, 저항 Rg와 Rf에 흐르는 전류는 같다. 저항 Rg에 흐르는 전류를 라고 할 때, Rg 흐르는 전류에 옴의 법칙을 적용해서 방정식을 세우면:

위 방정식에서 전류 는:

Vout에서 Rf에 흐르는 전류 에 대해 옴의 법칙을 적용해서 방정식을 세우면:

위의 방정식을 정리해서 이득을 구하면:

같이 보기

[편집]각주

[편집]- ↑ MAXIM Application Note 1108: Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs Archived 2007년 6월 26일 - 웨이백 머신 — Retrieved November 10, 2007

- ↑ “Analog devices MT-044 TUTORIAL” (PDF). 2014년 6월 10일에 원본 문서 (PDF)에서 보존된 문서. 2010년 10월 28일에 확인함.