결핍 영역

반도체 물리에서 결핍 영역(depletion region)이란 전도성을 띤 도핑된 반도체 물질에서 이동성 전하 운반자가 확산에 의해 빠져나갔거나 전기장에 의해 강제로 다른 곳으로 옮겨짐에 따라 만들어지는 절연된 영역을 뜻한다. 결핍 영역에는 이온화된 주개(donor)와 받개(acceptor) 불순물만 남는다. 결핍 영역을 결핍층(depletion layer), 결핍 구간(depletion zone), 접합 영역(junction region), 공간 전하 영역(space charge region), 공간 전하층(space charge layer) 같은 용어로 지칭하기도 하는데, 모두 같은 뜻이다. 분야마다 우리말 용어가 조금씩 다른데, 2010년 발표된 한국물리학회 공식용어 조정안에서는 결핍 영역을 한국어 표준 용어로 정했다. 일본어에서 같은 단어를 공핍층(空乏層)으로 옮기다 보니 한국어에서도 결핍 대신 공핍으로 옮기는 경우가 많다.

결핍 영역은 전도성이 있는 영역에서 자유 전하 운반체를 전부 없애서 전류를 운반할 수 있는 것을 모두 없애버렸기 때문에 그런 이름이 붙어 있다. 다이오드, 양극성 접합형 트랜지스터, 장효과 트랜지스터, 가변 전기용량 다이오드 같은 반도체 소자를 이해하기 위해서는 결핍 영역을 제대로 이해해야만 한다.

아래에서는 PN 접합과 MOSFET을 중심으로 설명하지만, 위에 언급한 소자에서 모두 결핍 영역이 생길 수 있다.

p-n 접합의 공핍 영역[편집]

PN 접합에서는 자연스럽게 결핍 영역이 생성된다. 열평형 상태, 또는 정상 상태에서는 시간에 따른 변화가 없기 때문에 그 특성이 쉽게 설명되는 편이긴 하지만, 이 평형 상태도 정적 평형 상태는 아니고 동적 평형 상태다.

전자든 양공이든, 마치 물 속에서 잉크가 물 전체의 잉크 농도가 균일하게 될 때까지 퍼져 나가듯이, 각각의 밀도가 낮은 쪽으로 확산되게 마련이다. N형, P형 반도체의 정의에 따라 N형 반도체에는 P형 영역에 비해 전자가 남아돌고, P형 반도체에는 N형 영역에 비해 양공이 남아돈다. 따라서 N 도핑된 반도체와 P 도핑된 반도체를 맞붙여서 접합을 만들면 전자는 P형 영역으로, 양공은 N형 영역으로 퍼져나간다. N 쪽에서 P 쪽으로 전자가 움직이고 나면 원래 전자가 있던 N 쪽에는 양전하를 띠는 주개 이온이, 마찬가지로 P 쪽에서 양공이 빠져나간 자리에는 음전하를 띠는 받개 이온이 남는다.[1] [2]

반대편으로 옮겨간 전자는 P 쪽에 있는 양공과 만나서 재결합하면서 사라지며, N 쪽에서 옮겨간 양공도 마찬가지로 사라진다. 그 결과 확산해서 이동한 전자와 양공은 사라지고, 움직일 수 있는 전하 운반자가 없는 경계면 부근(결핍 영역)에는 대전된 이온만 남는다. 따라서 결핍 영역의 N 쪽에는 양전하를 띠는 이온이, P 쪽에는 음전하를 띤 이온이 남고, 그 결과 전기장이 만들어진다. 이 때 전기장은 해당 영역에 많은 전하 운반자가 반대편으로 넘어가는 데 방해가 되는 방향으로 형성된다. 전하가 충분히 많이 확산되고 나면 그로 인해 형성되는 전기장이 더 이상 전하 운반자가 움직일 수 없을 만큼 강해지는데, 이 상태가 바로 결핍 영역이 평형에 이른 상태다. 결핍 영역에 걸린 전기장을 적분하면 내부 확산 전위(접합 전압, 장벽 전압, 접촉 전위 등으로도 부름)를 구할 수 있다.

- 수학적으로 풀어보면 반도체 소자에서 전하는 전기장에 의한 전도(표류 전류)와 확산 과정을 통해 전달된다. P형 영역에서 양공에 의해 전하가 전달될 때를 가정하면, 전기 전도도를 σ, 확산 상수를 D로 표기할 때 알짜 전류는 다음과 같은 식으로 쓸 수 있다.

- 여기에서 q는 기본 전하(1.6×10−19 쿨롱)를, p는 양공의 밀도(단위 부피당 개수)를 나타낸다. 전도의 효과에 의해 양공은 전기장 방향으로 힘을 받는다. 확산의 효과로는 전하 운반자가 밀도가 낮은 쪽으로 움직이기 때문에 양공의 경우에는 밀도 그래디언트가 양의 값을 가지는 방향으로 음의 전류가 흐르게 된다. (전자를 기준으로 한다면 양공 밀도 p를 전자 밀도 n으로 바꾸고 그 앞의 부호를 반대로 바꿔야 한다. 상황에 따라 전자와 양공을 전부 고려해야 할 수도 있다.) 동적 평형 상태에 이른 p-n 접합의 결핍 영역과 같이 두 전류 성분이 똑같으면 D와 σ 사이의 관계를 규정하는 아인슈타인 관계식에 의해 전류가 0이 된다.

(1) 역바이어스가 걸리면(P 쪽이 N 쪽보다 전압이 낮으면) 결핍 영역에서의 전위차가 더 커진다. 그러면 결핍 영역이 더 넓어지므로 표류 전류 성분은 늘어나고 확산 전류 성분은 줄어든다. 이 경우에는 위의 p-n 접합 그림을 기준으로 왼쪽으로 알짜 전류가 흐른다. 이 상황에서는 전류 밀도가 작기 때문에 아주 작은 역방향 포화 전류만 흐를 수 있다.

(2) 순방향 바이어스가 걸리면(P 쪽이 N 쪽보다 전압이 높으면) 결핍 영역이 좁아지고 전하 운반자를 주입하는 데 필요한 장벽이 낮아진다. 전류 중에서 확산 전류 성분이 크게 늘어나고 표류 전류는 줄어든다. 이 경우에는 위의 p-n 접합 그림을 기준으로 오른쪽으로 알짜 전류가 흐른다. 전류 밀도가 높기 때문에(바이어스 전압이 커지면 지수함수적으로 증가한다) 전합은 전도성을 띠게 되고 순방향으로 큰 전류가 흐를 수 있다. 이 전류는 수학적으로는 쇼클리 다이오드 공식으로 기술할 수 있다. 역바이어스가 걸렸을 때 전류가 거의 흐르지 않고 순방향 바이어스가 걸렸을 때 전류가 아주 많이 흐르는 특징은 정류기에 응용할 수 있다.

MOS 축전기의 결핍 영역[편집]

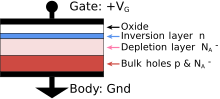

MOS 축전기에서도 결핍 영역을 볼 수 있다. 오른쪽 그림은 P형 기판 위에 만들어진 금속 산화물 반도체의 구조를 보여준다. 이 반도체는 원래 양공에 의한 전하가 받개 도핑 불순물에 의한 음전하와 정확하게 상쇄되는 전하 중성 특성을 가진다고 가정하자. 이 소자의 게이트에 Q 만큼의 양전하를 대전시켜서 양전압을 걸면 게이트에 가까운 쪽의 반도체에 있는 양전하를 띠는 양공이 게이트에 모인 전하에 의해 밀려나서 아래쪽에 있는 전기접촉을 통해 빠져나간다. 이러면 움직일 수 있는 양공은 다 빠져 나가서 절연성을 띠는 결핍된 영역이 남게 되고, 그 영역에는 움직이지 못하는 음전하를 띤 받개 불순물만 남는다. 게이트에 대전된 양전하가 많아질수록, 즉 게이트에 더 큰 양전압이 걸릴수록, 결과적으로 반도체 표면에서 빠져나가는 양공이 더 많을수록 결핍 영역은 더 커진다. (이 소자에서는 결핍폭의 상한이 정해져 있다. 그 상한은 표면 근방의 얇은 층인 채널에 있는 전하 운반체의 역전층이 형성되는 조건에 의해 결정된다. 지금은 역전층이 생기지 않을 정도로 충분히 낮은 양전압이 걸린 경우에 대해서만 생각하자.)

게이트 물질이 벌크 반도체의 반대 유형의 폴리실리콘일 때 게이트를 기판과 전기적으로 합선시키면 위에 있는 p-n 접합의 경우와 거의 비슷한 방식으로 자발적인 결핍 영역이 만들어진다.

결핍폭[편집]

반도체 내의 결핍 영역의 너비를 결핍폭(depletion width)이라고 부른다. 보통 p-n 접합이나 MOS 축전기처럼 1차원적인 구조를 가진 소자에서 주로 쓰이는 용어다. 결핍 영역의 너비는 전하 중성 원리에 따라 결정된다. 두 가지 예를 살펴보자.

p-n 접합의 결핍폭[편집]

전하 중성 원리는 양전하의 총합과 음전하의 총합이 같아야 된다는 원리다.

- ,

여기에서 n과 p는 자유 전자와 양공의 개수를 뜻하며, 와 는 각각 이온화된 주개와 받개 개수를 뜻한다. 완전히 이온화되는 경우에 가 만족된다면

라는 관계식을 얻을 수 있으며, 이 조건이 만족되면 받개에 의한 알짜 음전하량과 주개에 의한 알짜 양전하량이 균형을 이루게 된다. 이 때 결핍폭은 이다.

결핍폭을 유도하는 자세한 과정은 참고 문헌에서 찾아보도록 하자.[3] 유도 과정은 접합면에 수직인 방향으로 1차원 공간에서 프와송 방정식을 푸는 식으로 구성된다. 위쪽에 있는 그림에서도 확인할 수 있듯이 결핍 영역 밖에서는 전기장이 0이기 때문에 가우스의 법칙을 생각해 보면 이 절의 첫 번째 식으로 적어놓은 것처럼 각 영역에 있는 전하 밀도가 균형을 이뤄야 함을 알 수 있다. 각 영역별로 나눠서 각 영역의 전하 밀도를 각각의 프와송 방정식에 대입해 보면 결핍폭이 나오는데, 다음과 같은 식으로 주어진다.

여기에서 은 해당 반도체 물질의 상대 유전율이며 는 내부 확산 전위, 는 가해진 전압을 뜻한다. 결핍 영역의 폭은 N 쪽과 P 쪽이 다를 수 있는데, 도핑이 약할수록 결핍 영역이 넓어진다.[4] 결핍폭을 조금 더 정확하게 계산하려면 결핍 영역 가장자리에 여전히 전하 운반자가 약간은 남아있다는 점까지 고려해야 한다.[5] 그러한 점을 감안하면 위에 있는 마지막 괄호 안쪽에 -2kT/q 항을 추가해야 한다.

MOS 축전기의 결핍폭[편집]

p-n 접합과 마찬가지로 전하 중성 원리가 핵심이다. 기판이 P형이라고 해 보자. 게이트에 Q라는 양전하가 대전되어 양공이 w 깊이만큼 밀려나면 그만큼 음전하를 띤 받개 이온이 노출되어 게이트에 대전된 전하량과 균형을 이룬다. 받개 도펀트가 단위 부피당 개 있다고 가정하고 전하 중성을 따져 보면 결핍폭 w는 다음 식으로부터 구할 수 있다.

결핍폭이 충분히 넓어지면 반도체와 산화물 사이의 경계면에 역전층이라는 아주 얇은 층이 생기고, P형 물질에서 다수 운반자인 양공과 반대 전하를 띠는 전자가 나타날 수 있다. 역전층이 형성되면 게이트 전하량 Q가 커져도 결핍폭은 더 늘어나지 않는다. 이 때는 역전층에 들어가는 전자 수가 늘어가면서 전하 중성 조건이 만족된다. MOSFET에서는 역전층을 채널이라고 부른다.

결핍 영역의 전기장과 밴드 휨[편집]

결핍 영역과 연관된 개념으로 밴드 휨(band bending)이 있다. 밴드 휨은 결핍 영역의 전기장이 게이트에서의 최댓값인 에서 결핍 영역의 가장자리에서의 최솟값인 0으로 선형적으로 바뀌기 때문에 일어나는 현상이다.[6]

여기서 A는 게이트 면적이고 = 8.854×10−12 F/m이다. 식에 나와 있는 것처럼 전기장이 선형으로 변하면 전위는 2차함수 형태로 변화한다. 그 결과로 전위에 따라 에너지 준위와 에너지 밴드가 휘면서 밴드 휨이 발생한다.

같이 보기[편집]

참고 문헌[편집]

- ↑ Robert H. Bishop (2002). 《The Mechatronics Handbook》. CRC Press. ISBN 0-8493-0066-5.

- ↑ John E. Ayers (2003). 《Digital Integrated Circuits: Analysis and Design》. CRC Press. ISBN 0-8493-1951-X.

- ↑ Pierret, Robert F. (1996). 《Semiconductor Device Fundamentals》. 209 to 216쪽.

- ↑ Sasikala, B; Afzal Khan; S. Pooranchandra; B. Sasikala (2005). 《Introduction to Electrical , Electronics and Communication Engineering》. Firewall Media. ISBN 978-81-7008-639-0.

- ↑ Kittel, C; Kroemer, H. (1980). 《Thermal Physics》. W. H. Freeman. ISBN 0-7167-1088-9.

- ↑ Wayne M. Saslow (2002). 《Electricity, Magnetism, and Light》. Elsevier. ISBN 0-12-619455-6.

![{\displaystyle W\approx \left[{\frac {2\epsilon _{r}\epsilon _{0}}{q}}\left({\frac {N_{A}+N_{D}}{N_{A}N_{D}}}\right)\left(V_{bi}-V\right)\right]^{\frac {1}{2}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/9cf1e6d1a9bbf0cd58c76eba5749fa66b8556768)